# A Neural Network Approach for Calibrating Memristors Crossbars

Mohammad Rezaeifar, He Chaoyi, Kamran Entesari, Linda Katehi

MemSys2025-11th International Symposium on Memory Systems

October 7-8,2025

Washington D.C., USA

#### **Title**

- A Neural Network Approach for Calibrating Memristor Crossbars

- Mohammad Rezaeifar, He Chaoyi, Kamran Entesari, Linda Katehi

- Texas A&M University

- MemSys 2025 Washington, VA

### **Motivation**

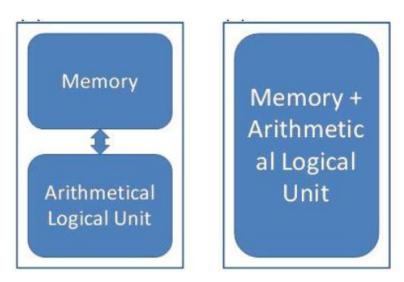

- Von Neumann bottleneck → costly data movement

- In-Memory Computing (IMC) with memristors = promising solution

- BUT: crossbars suffer IR-drop, parasitic effects, non-linearities

- Accuracy degradation in analog MVM

In memory & Von-Neumann computing

# **Problem Statement**

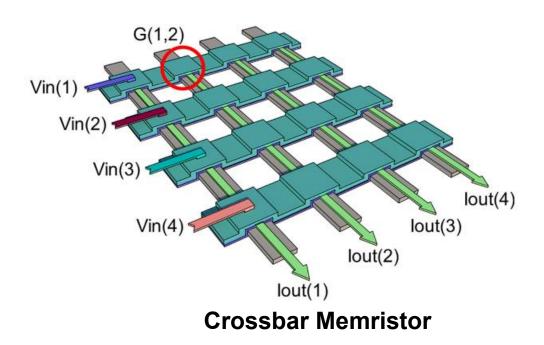

**Model of a Crossbar Memristor**

## Contributions

- Post-fabrication calibration (no hardware change)

- Neural network framework

- accuracy improvement (MSE reduction)

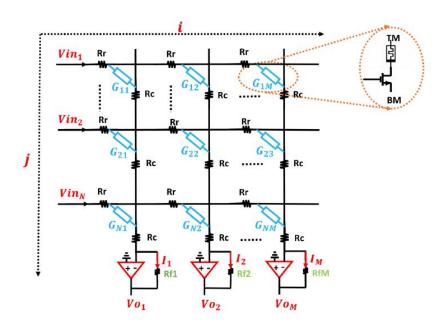

### **Crossbar Basics**

Row resistors V2

Column resistors V3

I1 I2 I3

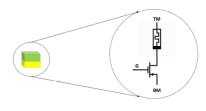

Figure 2: A memristor cell architecture integrating o sistor (1T) and one resistor (1R).

Figure 3: Memristor crossbar performing MVM. Conductance matrix G (size  $N \times M$ ) is multiplied by voltage input vector  $V_{in}$  (size  $1 \times N$ ).

Figure 1: A memristor crossbar array structure.

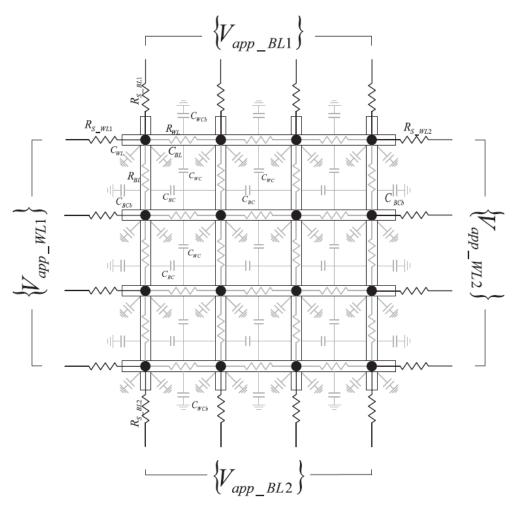

### **Sources of Errors**

- Wire resistance → IRdrop

- Capacitance/inductance

→ distortions

- Device variability → drift, noise

- Example: outputs deviate significantly from ideal MVM

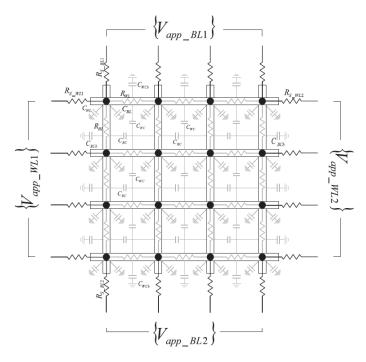

**Model of a Crossbar Memristor**

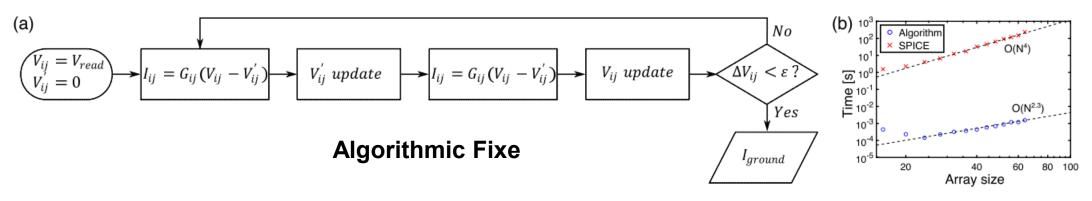

#### **Related Work**

- **Hardware fixes** → bigger area, higher complexity

- **Circuit-level** → error correction, compensation

- **Algorithmic** → retraining with hardware-aware models

- Still: incomplete + trade-offs

#### **Hardware Fixe**

$BL_1 BL_2$

$BL_1BL_2$

#### **Circuit-level Fixe**

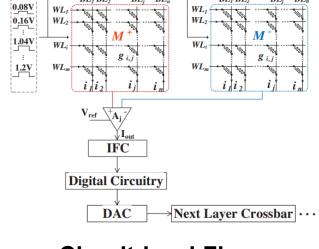

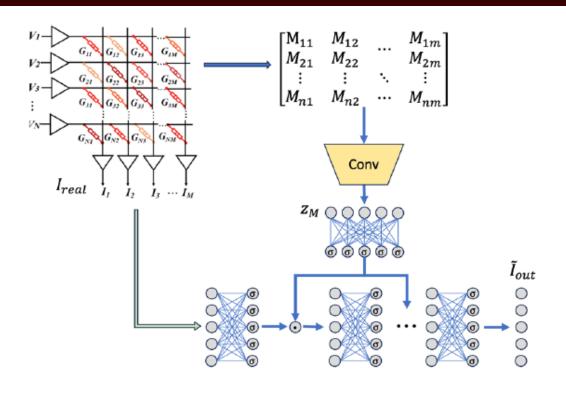

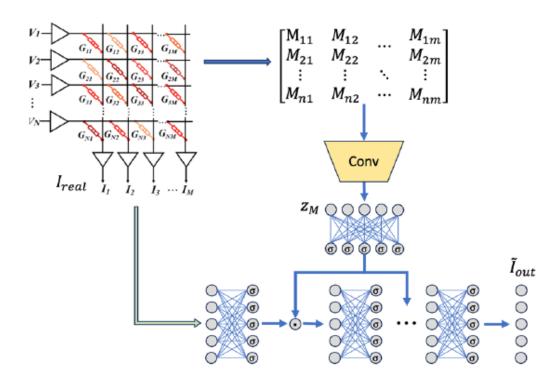

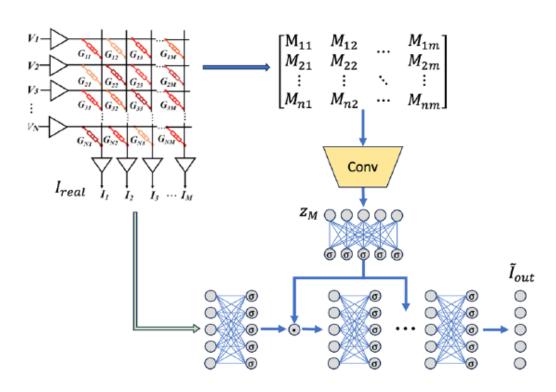

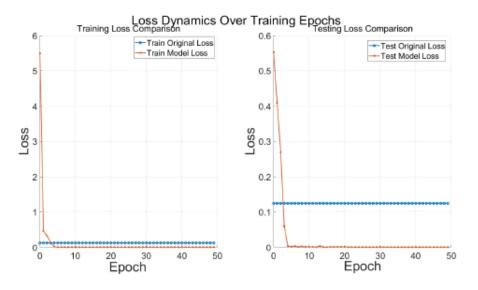

# Our Approach

- Learn systematic distortions with NN

- Input: Ideal conductance matrix (encode latent vector), Real measured currents

- Output: corrected, near-ideal currents

$$I_{\text{real}} = \mathcal{F}(M, V_{\text{in}}) + \varepsilon$$

(2)

$$\begin{split} \hat{I}_{\text{out}} &= \mathcal{G}(I_{\text{real}}, M) \equiv \mathcal{G}_{\theta}(I_{\text{real}}, M) = \tilde{I}_{\text{out}} \\ &\rightarrow \max_{\theta} p_{\theta}(\hat{I}_{\text{out}} | I_{\text{real}}, M) \\ &= \max_{\theta} p_{\theta}(\hat{I}_{\text{out}} | \mathcal{F}(M, V_{\text{in}}) + \epsilon, M) \end{split} \tag{3}$$

Figure 4: Model Structure

$$O_{i+1} = CS(O_i, z_m)$$

$$= (W_1O_i + b_1) \odot \sigma(W_2z_m + b_2) + W_3z_m,$$

$$i = 0, 1, 2, ..., N - 1,$$

(4)

#### Framework

- Step 1: Encode conductance matrix  $\rightarrow$  latent vector  $Z_m$

- Step 2: Used with measured output I<sub>real</sub>

- Step 3: Neural net calibration layers  $\rightarrow I_{out}$

- Activation = sigmoid

Figure 4: Model Structure

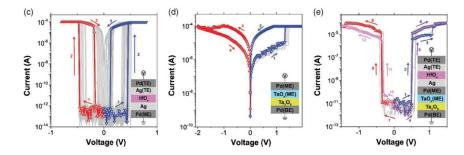

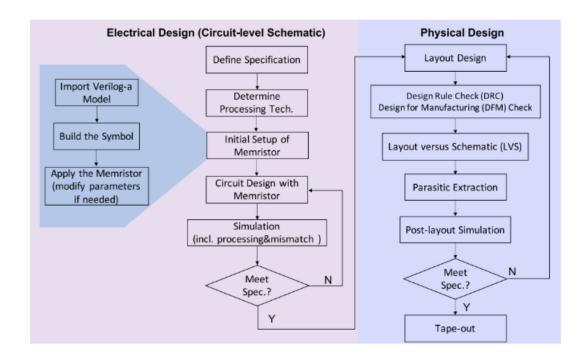

#### **Data Collection**

- Custom Verilog-A memristor model in Cadence Virtuoso

- Integrated with 22nm FD-SOI CMOS

- Dataset: 1,000 conductance matrices (16.6µS–100µS), 100 input vectors each (0.1–0.5V), → 100,000 VMM outputs

```

module analytical (p, n);

inout p, n;

electrical p, n;

parameter real Ap = 0.12340, An = -0.33000;

parameter real to = 2.74111, tn = 2.59685;

parameter real p0 = -40928.13784, p1 = 55117.97865;

parameter real m0 = 41366.35820, m1 = 7789.66771;

parameter real Rinit = 40000;

parameter real eta = 1;

parameter real ap=0.225, bp=4.12;

parameter real an=0.2801, bn=4.10;

real Rmp, Rmn, svp, svn, vin, RS, IVp, IVn, IV;

real first iteration, R0 last, dt, it;

analog function integer stp;

real arg; input arg;

stp = (arg >= 0 ? 1 : 0 ):

endfunction

analog begin

if (first iteration=0) begin

20.

R0 last=Rinit;

21.

22.

dt=$abstime-it;

Rmp=rp0+rp1*vin; Rmn=rn0+rn1*vin;

24.

25.

if (vin>0) begin

26.

svp=Ap*(-1+exp(abs(vin)/tp));

RS=(R0 last+svp*Rmp*(Rmp-R0 last)*dt)/(1+svp*(Rmp-

R0 last)*dt):

28.

else begin

29.

30.

svn=An*(-1+exp(abs(vin)/tn));

RS=(R0 last+svn*Rmn*(Rmn- R0 last)*dt)/(1+svn*(Rmn-

R0 last)*dt);

32.

end

33.

if (RS>=Rmp && vin>0)

RS=R0 last;

if (RS<=Rmn && vin<0)

RS-R0 last;

if (abs(vin)<=0.5)

RS-R0 last;

IVp=ap*(1/RS)*sinh(bp*vin);

IVn=an*(1/RS)*sinh(bn*vin);

IV=IVp*stp(vin)+IVn*stp(-vin);

39.

I(p, n)<+ IV;

R0 last=RS;

41.

first iteration=1;

42.

it=$abstime;

43. end

endmodule

```

#### **Neural Network Model**

- Non-linear inverse operator $G_{\theta}$

- Compensate: IR-drop, noise, device non-linearity

- Lightweight inference (offline training, fast runtime)

- Adaptable to drift/ageing with small calibration set

Figure 4: Model Structure

# **Training Setup**

- Training: random input vectors + random matrices

- Validation: sinusoidal input, FIR filter config

Figure 4: Model Structure

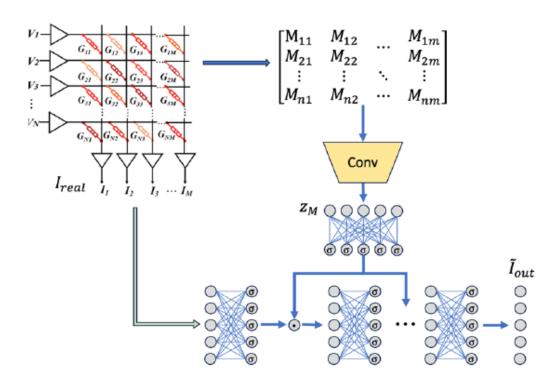

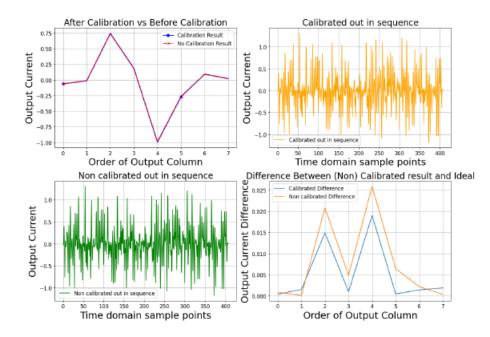

# Results (Training/Validation)

- MSE reduction ~1000× : Before calibration: 0.13 , After calibration: 1.4e-4

- Strong generalization to unseen signals

- Works with sinusoidal + DC inputs

Figure 6: Visualization of the calibration results compared with crossbar original output.

Table 1: Training and Testing MSE Performance for Different Input Type

| Input Data Type         | $(\tilde{I}_{out} - I_{ideal})^2)$ | $(I_{real} - I_{ideal})^2)$ |

|-------------------------|------------------------------------|-----------------------------|

| Training with Random    | 0.000139                           | 0.131878                    |

| Validating with Random  | 0.000149                           | 0.122114                    |

| Testing with Sinusoidal | 0.003398                           | 0.032687                    |

| Testing with DC Input   | 0.003185                           | 0.031794                    |

Figure 5: Training and Validating results

## Robustness

- Handles parasitic distortions + noise

- No frequent retraining needed

- Low overhead → only inference at runtime

# Comparison

- Device-level: area + complexity cost

- Circuit-level: partial corrections only

- Our method: post-fab, lightweight, scalable

#### **Future Work**

- Fabrication + Silicon validation Under noise, drift, temp.

- Extend to larger/tiled arrays (hierarchical calibration)

- Conditional fine-tuning for ageing effects

- Public release: Verilog-A

#### Conclusion

- Neural network framework → restores memristor accuracy

- Corrects distortions without hardware changes

- Enables practical, high-precision IMC systems

- Key step toward reliable neuromorphic computing

# Acknowledgments / Q&A

- Intelligent Electromagnetic Sensor Lab (IEMSL), Texas A&M

- Collaborators & advisors

- Thank you